Work/Project Experience

Qualcomm

Design Verification Engineer

Skills / Languages: C/C++, Python, SQL, OS, System Verilog/Verilog, ARM

I work on the CPU team to verify correct functionaliy and performance of ARM IP. My work focuses primarily on the C code running in a bare metal verification environment and analyzing the performace of our CPU cores.

Achievements:

- Built SQLite DB and lead the team in data pipeline flow and analysis

- Analyzed CPU data to generate new insights into improving L3 and CPU performance

- Wrote low level ARM assembly functions for multi processor synchronization in bare metal environment

- Created new library functions for interrupt handling and GIC programming

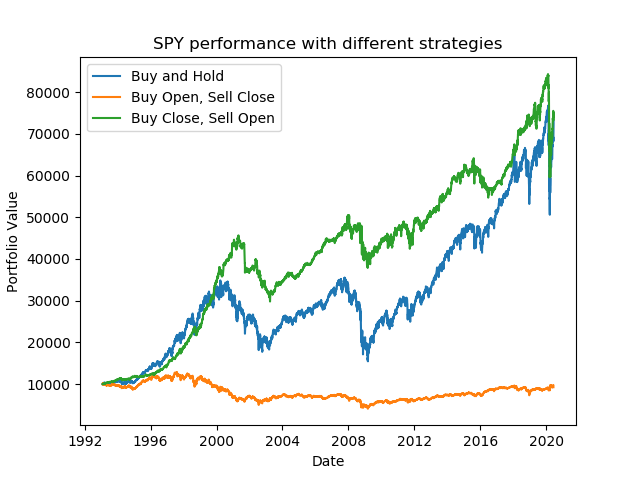

Stock Backtest platform

Self Project (Github)

Skills / Languages: Python, Object-oriented programming, Matplotlib, Pandas

I created a simple, easy-to-use stock market backtesting platform. The platform is designed to work primarily with OHLC data.

The project is based on Python and requires the "Pandas" package. It uses principles for OOP for easy strategy support.

I have also included two sample strategies that output buy orders into an excel spreadsheet. They can be easily adapted to fit to a stock broker or into the backtest platform.

For more actual documentation, visit the Github link above.

Achievements:

- Usable with any OHLC csv, such as those downloadable from Yahoo finance

- Simulates the any user strategy, implemented as a class, over the time period specified

- Graphs the data using Python matplotlib

HP Inc.

Asic Design Engineer

Skills / Languages: C/C++, Firmware, FPGA, System Verilog/Verilog

While at HP, I worked on the development of HP printer ASICS. The focus of my work was primarily on ASIC emulation using FPGAs.

I worked on synthesizing a working release of the ASIC design onto the FPGA. Firmware code can be run on this platform at slightly slower speeds than real silicon. This is allows code verification prior to ASIC silicon. I would often collaborate with firmware to debug code and HW running on my emulation platform. I was also responsible for the integration, design, and verification of a few RTL ASIC design modules.

Achievements:

- Created a new FPGA emulation platform with an integrated ARM CPU, which enabled ASIC HW verification as the DUT on FPGA and firmware development / verification on ARM pre-silicon

- Enhanced FW productivity by developing C test to verify various HW components

- Designed, integrated, and verified RTL modules in Verilog that eventually released in the ASIC

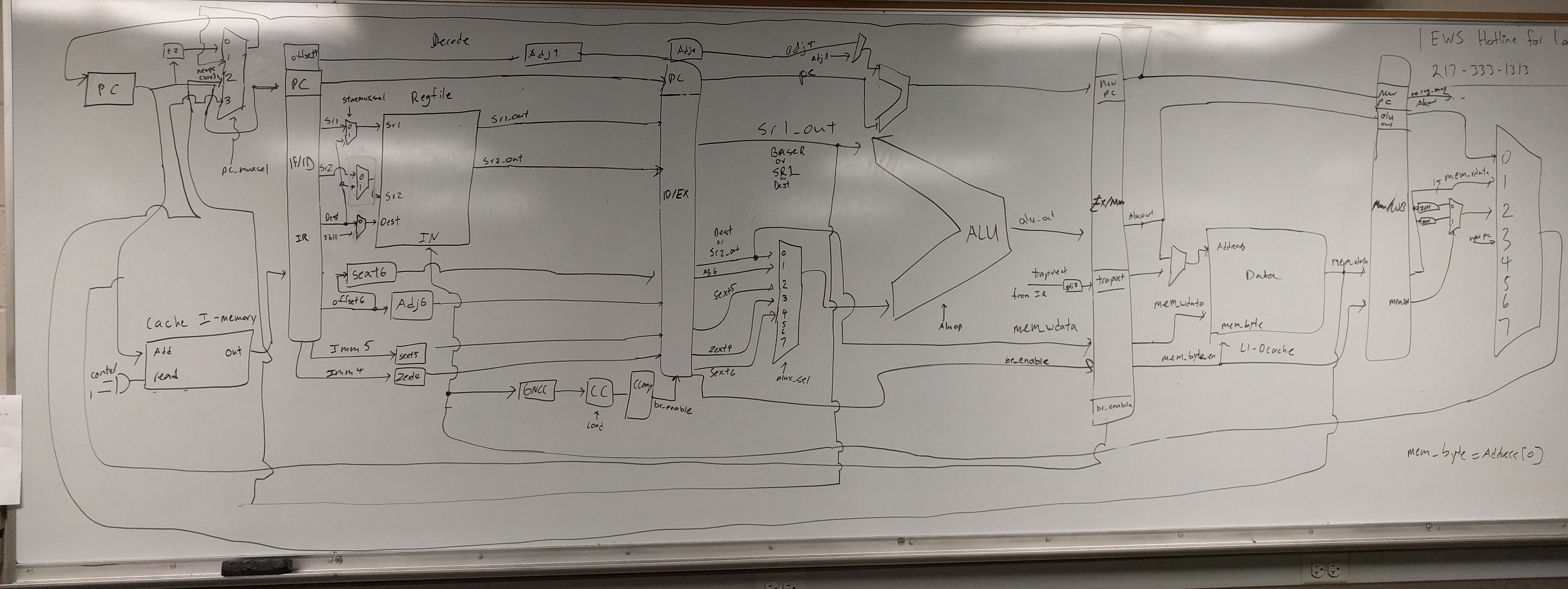

In-order LC3 CPU

School CPU project

Languages / Skills: Computer Architecture, Assembly, System Verilog

Design of a 5-stage in-order CPU with I/D L1 cache and unified L2 cache conforming to the LC-3b ISA.

In my computer architecture class, 2 others and I was tasked with designing the highest performing CPU conforming to the LC-3b ISA. Performance ranking amongst peers was one of the criteras for grading as well as, obviously, correctness.

I worked primarily on the design of the datapath section, while my partners worked on the cache design and performance measurement

Achievements:

- Implemented a dynamic branch predictor using the GAp prediction scheme with 8 way full associatve BTB, increasing performance by 25%

- Increased max frequency by analyzing critical path timing

- CPU design performance ranked top 10 in semester amonst 30ish teams